Improvement of power and density for RFID chips

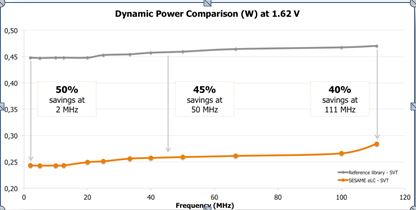

For RFID Tags, dynamic power is a critical factor as the capability for lower power translates immediately into a wider range of detection (RFID tag read range) and/or a highest identification rate in the same range. The main degree of freedom to improve power and area of RFID tag is located in the digital block. The SESAME eLC standard cell library enables up to 50% savings of dynamic power when compared to any other logic library available at 180 nm.

Such a comparison must be based on the Motu uta v6.0 benchmark with its Tsunami testbench (see results below), providing a quick and simple way to the expected improvement of overall performances of RFID tags.

Figure 1: SESAME eLC versus a free library - Dynamic power comparison at TSMC 180 nm G

Post-synthesis results, based on Motu-Uta V6 RTL benchmark – worst case conditions (SS 1.62V 125°C)

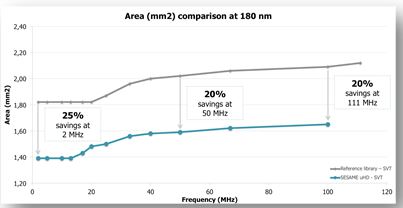

Conversely, if area saving is more critical, SESAME uHD library represents the best trade-off between high density and low power consumption. This library, which proudly claims to be the densest library available at 180nm, enables up to 25% area reduction (see figure below).

For RFID chip dominated by its digital area, the overall area saving represents the decisive incentive to opt for SESAME uHD library.

Figure 2: SESAME uHD versus free library - Silicon area comparison at TSMC 180 nm G

Post-synthesis results, based on Motu-Uta V6 RTL benchmark – worst case conditions (SS 1.62V 125°C)